## SGM4703 High-Power Stereo Class-D Audio Power Amplifier with Adjustable Power Limit and Automatic Level Control

#### SGM4703 GENERAL DESCRIPTION

The SGM4703 is a high-power, high-efficiency, stereo Class-D audio power amplifier with adjustable power limit (APL) and automatic level control (ALC). It operates with a wide range of supply voltages from 5V to 26V. With 24V supply voltage, it can deliver 2 × 40W peak output power for a pair of  $8\Omega$  speakers with 10% THD+N.

The high efficiency of SGM4703 extends battery life in playing music and allows it to deliver an output power of 2  $\times$  20W without the need for a bulky heat sink on a two-layer system board. Its high PSRR and low EMI emission reduce system design and manufacturing complexities, as well as lower system cost.

The SGM4703 features APL and ALC. The APL limits peak audio outputs to a user-defined value to protect audio speakers from excessive power dissipation or over-load. The APL and ALC adjust the voltage gain of the audio amplifiers in response to over-limit audio inputs, eliminating output clipping distortion while maintaining a maximally allowed dynamic range of audio outputs. The limiting voltage of APL and ALC can be either a user-defined value or the supply voltage.

The SGM4703 can be configured into driving either a pair of speakers in Bridge-Tied-Load (BTL) configuration for stereo applications or a single speaker in Parallel BTL (PBTL) configuration for mono applications.

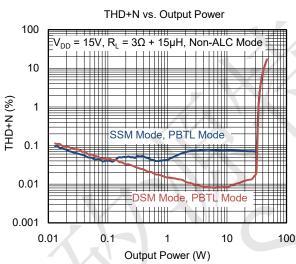

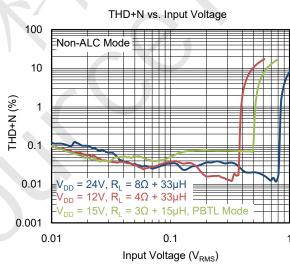

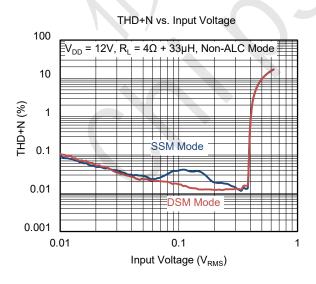

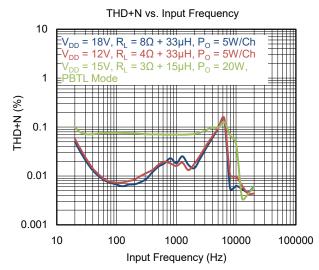

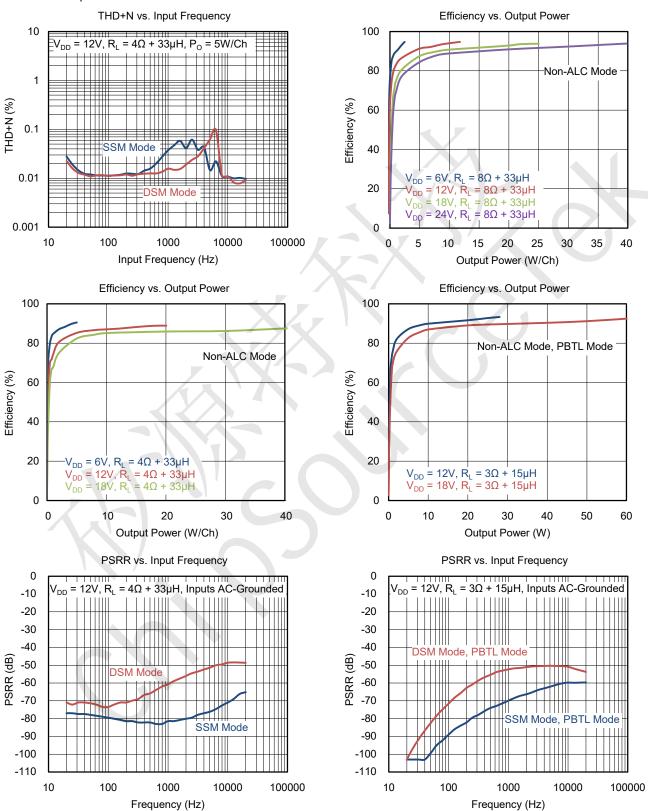

The SGM4703 features two PWM modulation schemes for Class-D audio amplifiers: Dual-Side-Modulation (DSM) and Single-Side-Modulation (SSM).

In SGM4703, comprehensive protection modes against various operating faults ensure its safe and reliable operation.

#### SGM4703 FEATURES

- Wide Range of Supply Voltages from 5V to 26V

- Adjustable Power Limit to Safeguard Audio Speakers

- Automatic Level Control to Eliminate Output Clipping

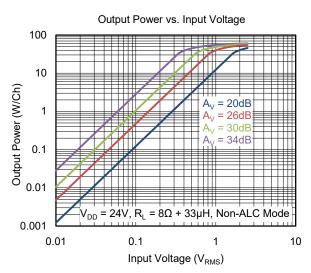

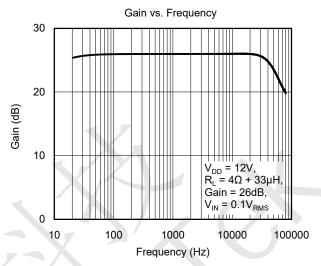

- Four Selectable Gain Settings: 20/26/30/34dB

- Three Selectable ALC Dynamic Characteristics

- Two Selectable PWM Frequencies with Optional Spread-Spectrum: 360kHz and 500kHz

- Two Selectable Modulation Schemes: SSM and DSM

- Optional PBTL Configuration for Mono Applications

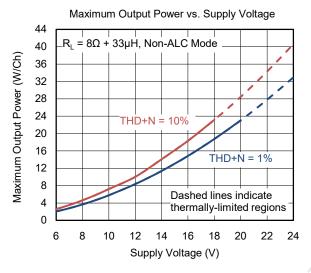

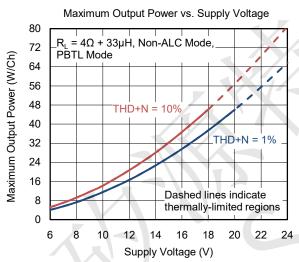

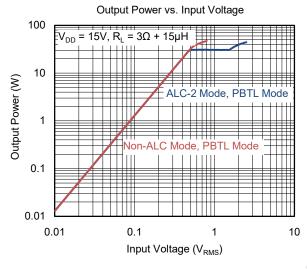

- Peak Output Power in Non-ALC

- 2 × 40W ( $V_{DD}$  = 24V,  $8\Omega$  + 33 $\mu$ H, BTL, THD+N = 10%)

- 2 × 32W ( $V_{DD}$  = 24V,  $8\Omega$  + 33 $\mu$ H, BTL, THD+N = 1%)

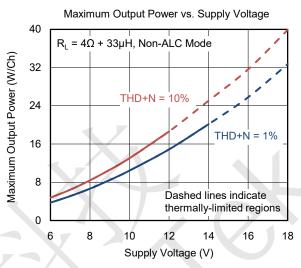

- 80W ( $V_{DD}$  = 24V,  $4\Omega$  + 33 $\mu$ H, PBTL, THD+N = 10%)

- 64W ( $V_{DD}$  = 24V,  $4\Omega$  + 33 $\mu$ H, PBTL, THD+N = 1%)

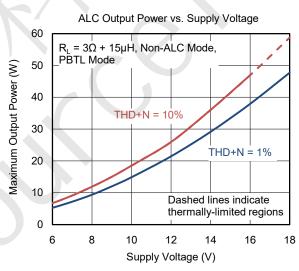

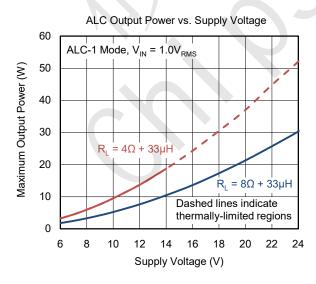

- ALC Output Power (THD+N < 0.5%) in ALC</li>

- 2 × 30W ( $V_{DD}$  = 24V,  $8\Omega$  + 33 $\mu$ H, BTL)

- 2 × 21W ( $V_{DD}$  = 15V,  $4\Omega$  + 33 $\mu$ H, BTL)

- 60W ( $V_{DD} = 24V, 4\Omega + 33\mu H, PBTL$ )

- Wide ALC Dynamic Range: 12dB (V<sub>DD</sub> = 12V)

- Low THD+N: 0.02% ( $V_{DD} = 24V$ ,  $8\Omega + 33\mu H$ ,  $P_0 = 20W/Ch$ )

- High PSRR: 80dB at 1kHz with SSM

- Protection Modes against Various Operating Faults Including Under-Voltage, Over-Voltage, Over-Current, Over-Temperature, and DC-Detect

1

Available in a Green TSSOP-28 (Exposed Pad)

Package

#### SGM4703 APPLICATIONS

Bluetooth/Wireless Speakers Consumer Audio Speakers Soundbars

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792 WEB:Http://www.ChipSourceTek.com

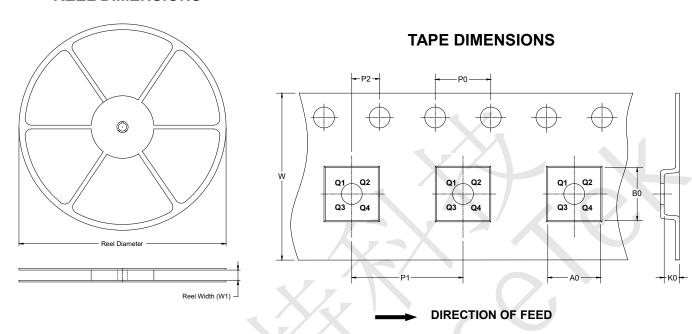

#### SGM4703 PACKAGE/ORDERING INFORMATION

| MODEL   | PACKAGE<br>DESCRIPTION    | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING         | PACKING<br>OPTION   |

|---------|---------------------------|-----------------------------------|--------------------|----------------------------|---------------------|

| SGM4703 | TSSOP-28<br>(Exposed Pad) | -40°C to +85°C                    | SGM4703YPTS28G/TR  | SGM4703<br>YPTS28<br>XXXXX | Tape and Reel, 4000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

XXXX

Vendor Code

Trace Code

Date Code - Year

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage Pins                     |                                  |

|-----------------------------------------|----------------------------------|

| AVDD, PVDD                              | 0.3V to 30V                      |

| Digital I/O Pins                        |                                  |

| EN, FAULTB                              | 0.3V to V <sub>AVDD</sub> + 0.3V |

| MODS                                    | 0.3V to $V_{GVDD}$ + 0.3V        |

| Analog Output Pins                      |                                  |

| GVDD                                    | 0.3V to 6.5V                     |

| ALC, GAIN, FREQ                         | 0.3V to V <sub>GVDD</sub> + 0.3V |

| Analog Input Pins                       |                                  |

| INPL/R, INNL/R, PLIMIT                  | 0.3V to $V_{GVDD}$ + 0.3V        |

| Package Thermal Resistance              |                                  |

| TSSOP-28 (Exposed Pad), θ <sub>JA</sub> | 28°C/W                           |

| Junction Temperature                    | +150°C                           |

| Storage Temperature Range               | 65°C to +150°C                   |

| Lead Temperature (Soldering, 10s)       | +260°C                           |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

#### SGM4703 RECOMMENDED OPERATING CONDITIONS

| PARAMETER                         | SYMBOL               | CONDITIONS                   | MIN            | TYP         | MAX               | UNITS     |  |

|-----------------------------------|----------------------|------------------------------|----------------|-------------|-------------------|-----------|--|

| Supply Voltage Range (1, 2)       | $V_{DD}$             | PVDD, AVDD                   | 5              |             | 26                | V         |  |

| Operating Ambient Temperature     | T <sub>A</sub>       |                              | -40            |             | 85                | °C        |  |

| Digital Input Valtage at EN       | V                    | Logic Low                    |                |             | 0.8               | V         |  |

| Digital Input Voltage at EN       | V <sub>EN</sub>      | Logic High                   | 2              |             | $V_{AVDD}$        | V         |  |

| Digital Input Valtage at MODS     | $V_{MODS}$           | Logic Low                    |                |             | 8.0               | V         |  |

| Digital Input Voltage at MODS     | V MODS               | Logic High                   | 2              |             | $V_{\text{GVDD}}$ | V         |  |

| Minimum Load Impedance (3)        | В                    | BTL Configuration (Stereo)   | 3.2            | 4           |                   | Ω         |  |

| I willimum Load impedance         | R∟                   | PBTL Configuration (Mono)    | 2              | 3           |                   | Ω         |  |

| Audio Input Capacitor             | C <sub>IN</sub>      | At INPL/R, INNL/R            | 0.1            | 1           | 2.2               | μF        |  |

| External Audio Input Resistor     | R <sub>INE</sub>     | At INPL/R, INNL/R            | 0              |             | 20                | kΩ        |  |

| Maximum Audio Input Voltage Level | V <sub>IN, MAX</sub> | At INNL/R, INPL/R            |                |             | 2.0               | $V_{RMS}$ |  |

| PLIMIT Voltage Range              | $V_{PLIMIT}$         | PLIMIT                       | 0              |             | $V_{\text{GVDD}}$ | V         |  |

| Maximum Load Current at GVDD      | I <sub>LOAD</sub>    | 4 - 3 X                      |                |             | 5                 | mA        |  |

| Supply Decoupling Capacitor       | C <sub>PVDD</sub>    | Ceramic                      | 0.1            | 1           |                   |           |  |

|                                   |                      | Electrolytic or Tantalum (4) | 100            | 220         |                   |           |  |

|                                   | C <sub>AVDD</sub>    | Ceramic                      |                | 1           |                   | μF        |  |

|                                   | $C_{GVDD}$           | Ceramic                      |                | 1           |                   |           |  |

|                                   | C <sub>PLIMIT</sub>  | Ceramic                      |                | 0.1         |                   |           |  |

| Bootstrap Holding Capacitor       | Св                   | At BSTPL/R, BSTNL/R          | 0.068          | 0.1         | 0.22              | μF        |  |

| Mono Mode Select                  | INNR INPR            | PBTL Configuration           | В              | oth Pins Sh | norted to GN      | ID        |  |

| Modulation Scheme Select          | MODS                 | Single-Side-Modulation (SSM) | High or Open   |             |                   |           |  |

| INIOQUIALION SCHEME SELECT        | MODS                 | Double-Side-Modulation (DSM) |                | L           | ow                |           |  |

|                                   |                      | 26dB                         |                | 0           | pen               |           |  |

| Voltage Gain Select               | CAIN                 | 30dB                         |                | Shorted     | to GND            |           |  |

| Voltage Gain Select               | GAIN                 | 34dB                         |                | 68kΩ        | to GND            |           |  |

|                                   |                      | 20dB                         |                | 300kΩ       | to GND            |           |  |

|                                   |                      | Non-ALC                      |                | O           | pen               |           |  |

| ALC Mode Select                   | ALC                  | ALC-1                        |                | Shorted     | to GND            |           |  |

| ALC Wode Select                   | ALC                  | ALC-2                        |                | 68kΩ        | to GND            |           |  |

|                                   |                      | ALC-3                        | 300kΩ to GND   |             |                   |           |  |

|                                   |                      | Constant Frequency at 360kHz |                | O           | pen               |           |  |

| DWM Fraguency Salast              | FREQ                 | 360kHz with Spread-Spectrum  | Shorted to GND |             |                   |           |  |

| PWM Frequency Select              | FREQ                 | Constant Frequency at 500kHz | 68kΩ to GND    |             |                   |           |  |

|                                   |                      | 500kHz with Spread-Spectrum  |                | 300kΩ       | to GND            |           |  |

#### NOTES:

- 1. The peak supply voltage including its tolerance over various operating conditions must not exceed its absolute-maximum-rated value (26V). Exposure to absolute-maximum-rated supply voltage may damage the device or affect device reliability permantly.

- 2. For high power applications, the maximum power supply  $V_{DD}$  that can be applied to the SGM4703 is largely limited by the thermal dissipation capability of the package and the system board layout.

- 3. The SGM4703 is specfied with an  $8\Omega$  resistive load in series with 33µH inductive load or with a  $4\Omega$  resistive load in series with 33µH inductive load or with a  $2\Omega$  or  $3\Omega$  resistive load in series with 15µH inductive load (in PBTL configuration). Without inductive loads, the maximum continous output power will severely suffer from efficiency and thermal degradation.

- 4. If the input supply is located more than a few centimeters from SGM4703, additional bulk capacitor may be required in addition to the ceramic capacitors.

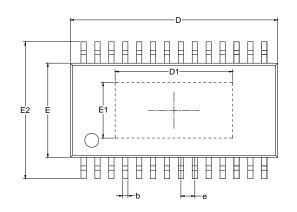

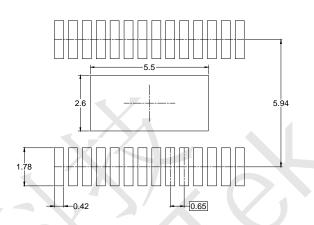

## **SGM4703 PIN CONFIGURATION**

TSSOP-28 (Exposed Pad)

#### **SGM4703 PIN DESCRIPTION**

| PIN | NAME   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                |

|-----|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

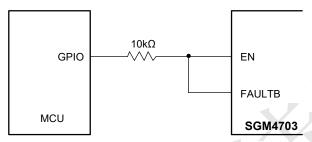

| 1   | EN     | DI   | Chip enable (active high) with an on-chip $250 k\Omega$ pull-down resistor to ground. A TTL logic input in compliance with AVDD.                                                                                                                           |

| 2   | FAULTB | DO   | Open-drain output indicating operational faults of OCP or DCP. Both faults can be set for auto-recovery by externally connecting FAULTB to EN. Otherwise, both OCP and DCP faults must be reset by cycling EN. A TTL logic output in compliance with AVDD. |

| 3   | INPL   | Al   | Left-channel non-inverting audio input biased at one half of GVDD.                                                                                                                                                                                         |

| 4   | INNL   | Al   | Left-channel inverting audio input biased at one half of GVDD.                                                                                                                                                                                             |

| 5   | GAIN   | AO   | Voltage gain select with an on-chip $250k\Omega$ pull-down resistor to ground. Connect to a resistor to ground to set the voltage gain of the audio amplifiers.                                                                                            |

| 6   | FREQ   | АО   | PWM frequency select with an on-chip $250k\Omega$ pull-down resistor to ground. Connect to a resistor to ground to set the PWM frequency with optional spread-spectrum.                                                                                    |

| 7   | AVDD   | Р    | Analog supply. Connect to a $1\mu F$ capacitor for decoupling. Also, add a decoupling resistor of $10\Omega$ between this pin and the system power supply for high-frequency filtering.                                                                    |

| 8   | AGND   | G    | Analog ground. Connect to the system power ground GND.                                                                                                                                                                                                     |

| 9   | GVDD   | АО   | Internally generated reference voltage at 5.6V. Connect to a 1µF capacitor for decoupling.                                                                                                                                                                 |

| 10  | PLIMIT | Al   | Adjustable power-limit. Connect to a resistor divider from GVDD to AGND to set the output voltage limit. Add a 0.1µF capacitor for decoupling.                                                                                                             |

| 11  | INNR   | Al   | Right-channel inverting audio input biased at one half of GVDD. Connect to ground (without decoupling capacitor) for mono mode in PBTL configuration.                                                                                                      |

| 12  | INPR   | Al   | Right-channel non-inverting audio input biased at one half of GVDD. Connect to ground (without decoupling capacitor) for mono mode in PBTL configuration.                                                                                                  |

| 13  | ALC    | АО   | ALC mode select with an on-chip $250k\Omega$ pull-down resistor to ground. Connect to a resistor to ground or leave open to set ALC dynamic characteristic.                                                                                                |

## **SGM4703 PIN DESCRIPTION (continued)**

| PIN            | NAME  | TYPE | DESCRIPTION                                                                                                                                                                     |

|----------------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14             | MODS  | DI   | PWM modulation select with an on-chip $250k\Omega$ pull-up resistor to GVDD. A TTL logic input in compliance with GVDD.                                                         |

| 15, 16         | PVDD  | Р    | Power supply inputs for the right-channel H-bridge. The power supplies for right-channel and left-channel H-bridges are internally.                                             |

| 17             | BSTPR | AO   | Connect to bootstrap holding capacitor for the right-channel non-inverting audio output, VOPR. A 0.1µF capacitor must be placed between this pin and VOPR for proper operation. |

| 18             | VOPR  | AO   | Right-channel non-inverting audio output terminal.                                                                                                                              |

| 19             | PGND  | G    | Power ground for the right-channel H-bridge. Connect to the system ground GND. The power ground for right-channel and left-channel H-bridges are internally shorted.            |

| 20             | VONR  | AO   | Right-channel inverting audio output terminal.                                                                                                                                  |

| 21             | BSTNR | AO   | Connect to a bootstrap holding capacitor for the right-channel inverting audio output, VONR. A 0.1µF capacitor must be placed between this pin and VONR for proper operation.   |

| 22             | BSTNL | AO   | Connect to a bootstrap holding capacitor for the left-channel inverting output, VONL. A 0.1µF capacitor must be placed between this pin and VONL for proper operation.          |

| 23             | VONL  | AO   | Left-channel inverting audio output terminal.                                                                                                                                   |

| 24             | PGND  | G    | Power ground for the left-channel H-bridge. Connect to the system ground GND. The power ground for right-channel and left-channel H-bridges are internally shorted.             |

| 25             | VOPL  | AO   | Left-channel non-inverting audio output terminal.                                                                                                                               |

| 26             | BSTPL | AO   | Connect to a bootstrap holding capacitor for the left-channel non-inverting output, VOPL. A 0.1µF capacitor must be placed between this pin and VOPL for proper operation.      |

| 27, 28         | PVDD  | Р    | Power supply inputs for the left-channel H-bridge. The power supplies for right-channel and left-channel H-bridges are internally shorted.                                      |

| Exposed<br>Pad | GND   | G    | Exposed pad. Connect to the system ground GND.                                                                                                                                  |

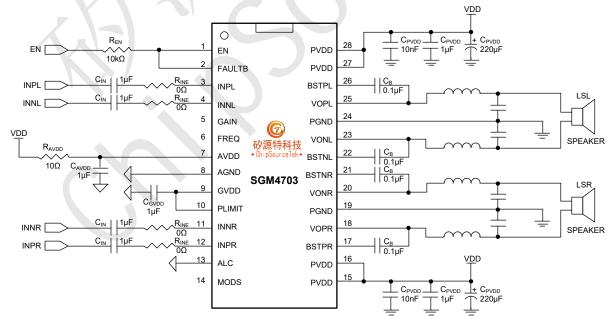

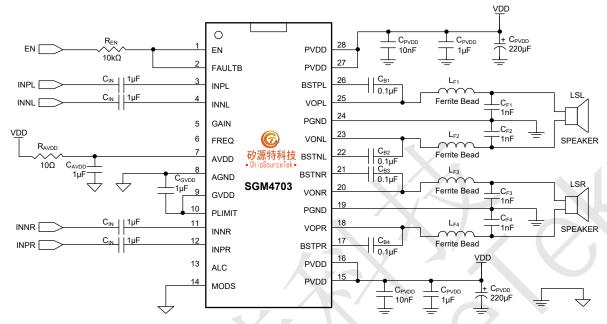

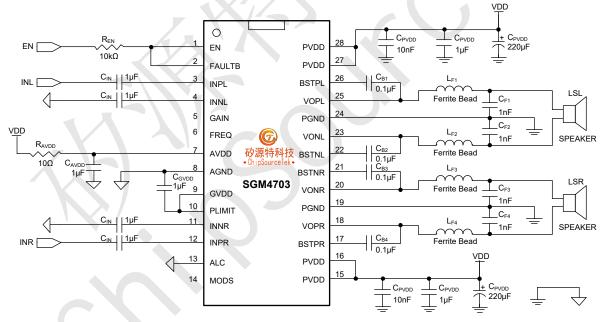

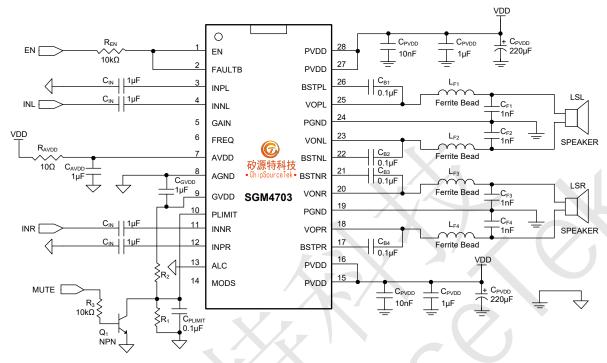

## **SGM4703 TYPICAL APPLICATION**

**Figure 1. Typical Application Circuit**

#### **SGM4703 IMPORTANT APPLICATION NOTES**

#### **Output Power Considerations**

- 1. The maximum output power of SGM4703 is determined primarily by the power supply (its output voltage and current) and speaker impedance. As a high power audio amplifier, the maximum output power of SGM4703 can be severely limited by the thermal dissipation capability of the system board layout.

- 2. The SGM4703 is packaged with an exposed thermal pad on the underside of the device. Solder the thermal pad directly onto a large grounded metal island (GND) underneath the package, as a thermal sink for proper thermal dissipation. On the grounded metal island, place several rows of solid, equally-spaced vias connecting to the bottom layer of the system board. Failure to do so can severely limit its thermal dissipation capability. It might even cause the device going into over-temperature shutdown occasionally.

- 3. Use wide open areas around the SGM4703 on the top and bottom layers of the system board as the ground plane GND. Place lots of solid vias connecting the top and bottom layers of GND. Furthermore, for proper thermal dissipation, reserve wide and uninterrupted GND areas along the thermal flow on the top layer, i.e., no wires cutting through the GND layer and obstructing the thermal flow in the proximity of the device.

- 4. All the power ground pins PGND are directly shorted to the ground plane GND as a central "star" ground for the SGM4703. Use a single point of connection between the analog ground AGND and the ground plane GND to minimize the coupling of high-current switching noise onto audio signals.

- 5. The power supply pins, PVDD, for the audio amplifiers' output stages are directly connected together with short and wide metal traces.

- 6. Use direct and low-impedance traces from the audio outputs (VOPL/R and VONL/R) to their individual output filters and speakers.

#### Output Filter Considerations

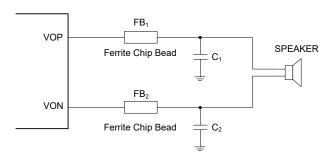

- 7. For most applications, the SGM4703 does not require an LC output filter when speaker wires are less than 10cm.

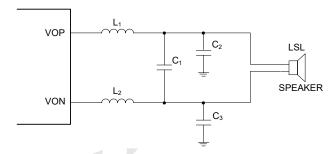

- 8. A ferrite bead filter constructed from a ferrite bead and a ceramic capacitor can be used to suppress EMI. Choose a ferrite bead with a rated current no less than 4A for  $8\Omega$  loads, 7A for  $4\Omega$  loads, and 9A for  $3\Omega$  or less loads (in PBTL configuration). Place the filter tightly together and as close as possible to the audio amplifier's output pins. A ferrite bead filter can also reduce high-frequency interference.

- 9. For applications where EMC requirements are extremely stringent or speaker wires are long, use a second-order LC lowpass filter. Place the filter tightly together and as close as possible to the audio amplifier's output pins. The LC output filter must be designed specifically for the speaker load since the load impedance affects the quality factor of the filter.

#### **General Considerations**

- 10. The SGM4703 requires adequate power supply decoupling to ensure its peak output power, high efficiency, low distortion, and low EMI emissions. Place each supply decoupling capacitor as individually close as possible to AVDD and PVDD pins.

- 11. Place a small decoupling resistor ( $10\Omega$ ) between the system power supply and AVDD to prevent high frequency Class-D transient spikes from interfering with the on-chip linear amplifiers.

- 12. For best noise performance, use differential inputs from the audio source for SGM4703. In single-ended input applications, the unused inputs of SGM4703 must be AC-grounded at the audio source. Also, take care to match the impedances seen at two differential inputs closely.

- 13. The maximum input signal dictates the required voltage gain to achieve the desired maximum output power. For best noise performance, consider a voltage gain as low as possible.

- 14. Do not alter the logic state of the MODS pin while the device is in operation. To change the setting of the pin, the device must be first brought into shutdown mode by pulling the EN pin low for at least 10ms before it can be restored to its normal operation.

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792 WEB:Http://www.ChipSourceTek.com

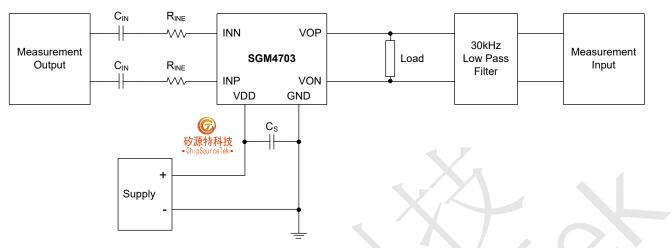

## SGM4703 TEST SETUP FOR ELECTRICAL AND PERFORMANCE CHARACTERISTICS

Figure 2. Test Setup Diagram

All parameters specified in Electrical and Typical Performance Characteristics sections are measured according to the conditions:

- 1. The two differential inputs are shorted for common-mode input voltage measurement. All other parameters are taken with input resistors  $R_{\text{INE}} = 0 \text{k}\Omega$  and input capacitors  $C_{\text{IN}} = 1 \mu \text{F}$ , unless otherwise specified.

- 2. The supply decoupling capacitors  $C_S = 2 \times (10nF + 1\mu F + 220\mu F)$  are placed close to the device.

- 3. A 33µH inductor was placed in series with the load resistor to emulate a speaker load for all AC and dynamic parameters.

- 4. The 33kHz lowpass filter is added even if the analyzer has an internal lowpass filter. An RC lowpass filter (1k $\Omega$ , 4.7nF) is used on each output for the data sheet graphs.

#### SGM4703 ELECTRICAL CHARACTERISTICS

$(V_{DD}=12V,f=1kHz,Load=4\Omega+33\mu H,C_{IN}=4\times1\mu F,R_{INE}=4\times0\Omega,GAIN=NC~(A_{V}=26dB),FREQ=NC~(f_{PWN}=360kHz),MODS=NC~(SSM),ALC~shorted~to~GND~(ALC-1),V_{PLIMIT}=V_{GVDD},C_{PVDD}=2\times(10nF+1\mu F+220\mu F),C_{AVDD}=1\mu F,C_{GVDD}=1\mu F,C_{B}=4\times0.1\mu F,both~channels~driven,T_{A}=+25^{\circ}C,unless~otherwise~specified.)$

| PARAMETER                            | SYMBOL               | CONDITIONS                                         | MIN | TYP  | MAX               | UNITS |

|--------------------------------------|----------------------|----------------------------------------------------|-----|------|-------------------|-------|

| Supply Voltage                       | $V_{DD}$             | PVDD, AVDD                                         | 5   |      | 26                | V     |

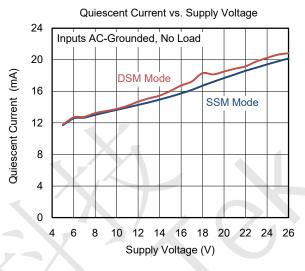

| Supply Quiescent Current             | I <sub>VDD</sub>     | Inputs AC-grounded, No Load                        |     | 15   |                   | mA    |

| Mute Current                         | I <sub>MUTE</sub>    | PLIMIT = GND, No Load                              |     | 8    |                   | mA    |

| 01                                   | İ .                  | SSM                                                |     | 36   |                   |       |

| Shutdown Current                     | I <sub>SD</sub>      | EN = 0V                                            | 1 7 | 58   |                   | μΑ    |

| Supply Voltage UVLO Detection        | V <sub>UVLOUP</sub>  | V <sub>DD</sub> Rising                             | XX  | 4.6  |                   | V     |

| Supply Voltage UVLO Release          | $V_{UVLODN}$         | V <sub>DD</sub> Falling                            |     | 4.3  |                   | V     |

| Supply Voltage OVP Detection         | V <sub>OVPUP</sub>   | V <sub>DD</sub> Rising                             |     | 28   |                   | V     |

| Supply Voltage OVP Release           | V <sub>OVPDN</sub>   | V <sub>DD</sub> Rising                             |     | 26.5 |                   | V     |

| Voltage Regulator Output             | $V_{\text{GVDD}}$    | No Load                                            |     | 5.6  |                   | V     |

| Input Common-Mode Bias               | $V_{COMM}$           | INPL/R, INNL/R                                     |     | 2.8  |                   | V     |

| Digital "Low" Input Voltage          | V <sub>IL</sub>      | EN, MODS                                           |     |      | 0.8               | V     |

| Divital filling 7 Lange (A.C.)       | .,                   | EN                                                 | 2.0 |      | V <sub>AVDD</sub> | .,    |

| Digital "High" Input Voltage         | V <sub>IH</sub>      | MODS                                               | 2.0 |      | $V_{GVDD}$        | V     |

| Digital "Low" Output Voltage         | V <sub>OL</sub>      | FAULTB, $R_{PULLUP} = 100k\Omega$ , $V_{DD} = 18V$ | AX  |      | 0.4               | V     |

| Pull-Down Resistor to Ground         | R <sub>DOWN</sub>    | EN, ALC, GAIN, FREQ                                |     | 250  |                   | kΩ    |

| Pull-Up Resistor to G <sub>VDD</sub> | R <sub>UP</sub>      | MODS                                               |     | 250  |                   | kΩ    |

| Output Resistance in Shutdown        | R <sub>OUT-SD</sub>  | At VOPL/R, VONL/R, EN = Low                        |     | 5    |                   | kΩ    |

|                                      | $V_{\sf GAIN}$       | Open                                               |     | 2.5  |                   |       |

| Voltage Level at                     |                      | Shorted to GND                                     | ,   | 0    |                   | 1 .,  |

| GAIN, FREQ, ALC Pins                 | $V_{FREQ} \ V_{ALC}$ | 68kΩ to GND                                        |     | 0.55 |                   | V     |

| Д.                                   |                      | 300kΩ to GND                                       |     | 1.40 |                   |       |

|                                      |                      | Open                                               |     | 30   |                   |       |

| Internal Input Resistance at         |                      | $R_{GAIN} = 0k\Omega$                              |     | 20   |                   |       |

| INPL/R, INNL/R Pins                  | R <sub>INI</sub>     | $R_{GAIN} = 68k\Omega$                             |     | 12   |                   | kΩ    |

|                                      |                      | $R_{GAIN} = 300k\Omega$                            |     | 60   |                   |       |

|                                      |                      | Open                                               |     | 26   |                   |       |

|                                      |                      | $R_{GAIN} = 0k\Omega$                              |     | 30   |                   | 1     |

| Voltage Gain                         | $A_{V}$              | $R_{GAIN} = 68k\Omega$                             |     | 34   |                   | dB    |

|                                      |                      | $R_{GAIN} = 300k\Omega$                            |     | 20   |                   |       |

|                                      |                      | Open or $R_{FREQ} = 0k\Omega$                      |     | 360  |                   |       |

| PWM Frequency                        | f <sub>sw</sub>      | $R_{FREQ} = 68k\Omega$ or $R_{FREQ} = 300k\Omega$  |     | 500  |                   | kHz   |

|                                      |                      | Dual BTL Configuration                             |     | 8.8  |                   | A/Ch  |

| Over-Current Limit                   | I <sub>LIMIT</sub>   | PBTL Configuration                                 |     | 13   |                   | Α     |

| Over-Temperature Threshold           | T <sub>OTSD</sub>    |                                                    |     | 160  |                   | °C    |

| Over-Temperature Hysteresis          | T <sub>HYS</sub>     |                                                    |     | 20   |                   | °C    |

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792 WEB:Http://www.ChipSourceTek.com

## SGM4703 ELECTRICAL CHARACTERISTICS (continued)

$(V_{DD}=12V,f=1kHz,Load=4\Omega+33\mu H,C_{IN}=4\times1\mu F,R_{INE}=4\times0\Omega,GAIN=NC~(A_{V}=26dB),FREQ=NC~(f_{PWN}=360kHz),MODS=NC~(SSM),ALC~shorted~to~GND~(ALC-1),V_{PLIMIT}=V_{GVDD},C_{PVDD}=2\times(10nF+1\mu F+220\mu F),C_{AVDD}=1\mu F,C_{GVDD}=1\mu F,C_{B}=4\times0.1\mu F,both~channels~driven,T_{A}=+25^{\circ}C,unless~otherwise~specified.)$

| PARAMETER                                                | SYMBOL               | CONDITIONS                                        |                                                 | MIN | TYP  | MAX               | UNITS         |

|----------------------------------------------------------|----------------------|---------------------------------------------------|-------------------------------------------------|-----|------|-------------------|---------------|

| Class-D Amplifier (V <sub>DD</sub> = 12V, R <sub>L</sub> | = 4Ω + 33μH,         | Both Channels Driven)                             |                                                 | •   | •    |                   |               |

| Maximum Output Power                                     | P <sub>O, MAX</sub>  | THD+N = 1%                                        |                                                 |     | 15   |                   | W/Ch          |

| ALC Output Power                                         | P <sub>O, ALC</sub>  | $V_{IN} = 0.50V_{RMS}$                            |                                                 |     | 13   |                   | W/Ch          |

|                                                          |                      | D = 4)M/Ob Non Al C Mada                          | SSM                                             |     | 0.04 |                   |               |

|                                                          |                      | P <sub>O</sub> = 1W/Ch, Non-ALC Mode              | DSM                                             | 7   | 0.02 |                   |               |

| Total Harmonic Distortion + Noise                        | THD+N                | D = 10M/Ch Non ALC Mode                           | SSM                                             | (A  | 0.02 |                   | %             |

| Total Harmonic Distortion + Noise                        | I DU+IN              | P <sub>0</sub> = 10W/Ch, Non-ALC Mode             | DSM                                             |     | 0.02 |                   | 70            |

|                                                          |                      | V <sub>IN</sub> = 0.50V <sub>RMS</sub> , ALC Mode | SSM                                             | 4   | 0.3  |                   |               |

|                                                          |                      | V <sub>IN</sub> – 0.50V <sub>RMS</sub> , ALC Mode | DSM                                             |     | 0.3  |                   |               |

| Dower Efficiency                                         |                      | P <sub>o</sub> = 10W/Ch, Non-ALC Mode             |                                                 | 3/  | 86   |                   | %             |

| Power Efficiency                                         | η                    | V <sub>IN</sub> = 0.50V <sub>RMS</sub> , ALC Mode |                                                 |     | 87   |                   | 70            |

| Output Offset Voltage                                    | Vos                  | No Load                                           |                                                 |     | ±20  |                   | mV            |

| Idle-Channel Noise                                       | V <sub>N</sub>       | Inputs AC-Grounded, A-weight                      | ed                                              |     | 145  |                   | $\mu V_{RMS}$ |

| Signal-to-Noise Ratio                                    | SNR                  | Maximum Output (7V <sub>RMS</sub> ), A-we         | eighted                                         |     | 94   |                   | dB            |

| Dower Supply Pointin Patio                               | PSRR                 | SSM                                               | f = 1kHz                                        |     | 80   |                   | dB            |

| Power Supply Rejection Ratio                             | FORK                 | DSM                                               | f = 1kHz                                        |     | 60   |                   | uБ            |

| Common Mode Rejection Ratio                              | CMRR                 | $f = 1kHz$ , $V_{IN} = 0.2V_{RMS}$                | f = 1kHz, V <sub>IN</sub> = 0.2V <sub>RMS</sub> |     | 60   |                   | dB            |

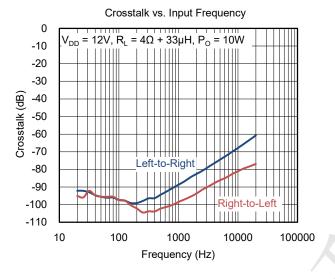

| Channel Separation                                       | Crosstalk            | P <sub>O</sub> = 10W, f = 1kHz                    |                                                 |     | 85   |                   | dB            |

| ,                                                        | A <sub>MAX</sub>     | V <sub>DD</sub> = 12V                             |                                                 |     | 12   |                   |               |

| Maximum ALC Attenuation                                  |                      | V <sub>DD</sub> = 15V                             |                                                 |     | 10   |                   | dB            |

|                                                          |                      | V <sub>DD</sub> = 18V                             |                                                 |     | 8.5  |                   |               |

| Startup Time                                             | t <sub>STARTUP</sub> | Including Fade-In Time                            |                                                 |     | 45   |                   | ms            |

| Shutdown Settling Time                                   | t <sub>SD</sub>      | Including Fade-Out Time                           |                                                 | 10  |      |                   | ms            |

| Adjustable Power Limit (APL)                             |                      |                                                   |                                                 |     |      |                   |               |

| Mute Mode                                                |                      |                                                   |                                                 |     |      | 0.3               | V             |

| APL Mode                                                 | $V_{PLIMIT}$         | $V_{GVDD} = 5.6V, V_{DD} = 24V, Load$             | = 4Ω + 33μH                                     | 0.7 |      | 3.5               | V             |

| ALC Mode                                                 |                      | V <sub>GVDD</sub> = 5.6V                          |                                                 | 4.5 |      | $V_{\text{GVDD}}$ | V             |

| Output Limit Voltage                                     | V <sub>LIMIT</sub>   | $V_{PLIMIT} = 1.5V$ , Load = $4\Omega + 33\mu$    | ıΗ                                              |     | 9.0  |                   | V             |

| DC Current Protection (DCP)                              |                      |                                                   |                                                 |     |      |                   |               |

| DC-Detect Threshold                                      |                      | $V_{DD} = 12V$ , Load = $4\Omega + 33\mu H$       |                                                 |     | 2.4  |                   |               |

|                                                          | $V_{DCP}$            | $V_{DD}$ = 15V, Load = $4\Omega + 33\mu H$        |                                                 |     | 3.0  |                   | V             |

|                                                          |                      | $V_{DD} = 18V$ , Load = $4\Omega + 33\mu H$       |                                                 |     | 3.6  |                   | 1             |

| Fade-In and Fade-Out                                     |                      |                                                   |                                                 | •   | •    | •                 | •             |

| Fade-In Time                                             | t <sub>FADEIN</sub>  |                                                   |                                                 |     | 8    |                   | ms            |

| Fade-Out Time                                            | t <sub>FADEOUT</sub> |                                                   |                                                 |     | 5    |                   | ms            |

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792 WEB:Http://www.ChipSourceTek.com

## **SGM4703 ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}$  = 15V, f = 1kHz, Load =  $4\Omega$  +  $33\mu$ H, SSM, both channels driven,  $T_A$  = +25°C, unless otherwise specified.)

| PARAMETER                         | SYMBOL               | CONDITIONS                                        | MIN | TYP  | MAX | UNITS  |

|-----------------------------------|----------------------|---------------------------------------------------|-----|------|-----|--------|

| Peak Output Power (1)             | D                    | THD+N = 10%, Non-ALC Mode                         |     | 27   |     | W/Ch   |

|                                   | P <sub>O, PEAK</sub> | THD+N = 1%, Non-ALC Mode                          |     | 23   |     | VV/CII |

| ALC Output Power                  | P <sub>O, ALC</sub>  | $V_{DD} = 15V, V_{IN} = 0.60V_{RMS}$              |     | 21   |     | W/Ch   |

| Total Harmonic Distortion + Noise | THD+N                | P <sub>O</sub> = 15W/Ch, Non-ALC Mode             |     | 0.02 |     | %      |

| Total Harmonic Distortion + Noise |                      | V <sub>IN</sub> = 0.60V <sub>RMS</sub> , ALC Mode |     | 0.3  |     | 70     |

| Power Efficiency (2)              | η                    | P <sub>O</sub> = 15W/Ch, Non-ALC Mode             |     | 85   |     | - %    |

| Power Efficiency V                |                      | V <sub>IN</sub> = 0.60V <sub>RMS</sub> , ALC Mode |     | 86   |     |        |

| Signal-to-Noise Ratio             | SNR                  | P <sub>O</sub> = 20W/Ch, A-weighted               |     | 95   |     | dB     |

$(V_{DD}$  = 18V, f = 1kHz, Load =  $8\Omega$  + 33 $\mu$ H, SSM, both channels driven,  $T_A$  = +25 $^{\circ}$ C, unless otherwise specified.)

| PARAMETER                         | SYMBOL              | CONDITIONS                                        | MIN | TYP  | MAX | UNITS |

|-----------------------------------|---------------------|---------------------------------------------------|-----|------|-----|-------|

|                                   | 0                   | THD+N = 10%, Non-ALC Mode                         |     | 22   |     | W/Ch  |

| Peak Output Power (1)             | $P_{O, PEAK}$       | THD+N = 1%, Non-ALC Mode                          |     | 18   |     | W/Cn  |

| ALC Output Power                  | P <sub>O, ALC</sub> | $V_{IN} = 0.70V_{RMS}$                            |     | 16   |     | W/Ch  |

| Total Harmonic Distortion + Noise | THD+N               | P <sub>O</sub> = 10W/Ch, Non-ALC Mode             |     | 0.02 |     | %     |

| Total Harmonic Distortion + Noise |                     | V <sub>IN</sub> = 0.70V <sub>RMS</sub> , ALC Mode |     | 0.3  |     | 70    |

| Davier <b>F</b> #inian av (2)     | η                   | P <sub>O</sub> = 10W/Ch, Non-ALC Mode             |     | 90   |     | - %   |

| Power Efficiency (2)              |                     | V <sub>IN</sub> = 0.70V <sub>RMS</sub> , ALC Mode |     | 91   |     |       |

| Signal-to-Noise Ratio             | SNR                 | P <sub>O</sub> = 15W/Ch, A-weighted               |     | 97   |     | dB    |

$(V_{DD} = 24V, f = 1kHz, Load = 8\Omega + 33\mu H, SSM, both channels driven, T_A = +25^{\circ}C, unless otherwise specified.)$

| PARAMETER                         | SYMBOL              | CONDITIONS                                       | MIN | TYP  | MAX | UNITS  |

|-----------------------------------|---------------------|--------------------------------------------------|-----|------|-----|--------|

| Peak Output Power (1)             | D                   | THD+N = 10%, Non-ALC Mode                        |     | 40   |     | W/Ch   |

|                                   | $P_{O, PEAK}$       | THD+N = 1%, Non-ALC Mode                         |     | 32   |     | VV/CII |

| ALC Output Power                  | P <sub>O, ALC</sub> | V <sub>IN</sub> = 1.0V <sub>RMS</sub>            |     | 30   |     | W/Ch   |

| Total Harmonic Distortion + Noise | THD+N               | P <sub>O</sub> = 20W/Ch, Non-ALC Mode            |     | 0.02 |     | %      |

| Total Harmonic Distortion + Noise |                     | V <sub>IN</sub> = 1.0V <sub>RMS</sub> , ALC Mode |     | 0.3  |     | 70     |

| Power Efficiency (2)              | η                   | Po = 20W/Ch, Non-ALC Mode                        |     | 90   |     | - %    |

| Power Efficiency V                |                     | V <sub>IN</sub> =1.0V <sub>RMS</sub> , ALC Mode  |     | 91   |     |        |

| Signal-to-Noise Ratio             | SNR                 | P <sub>0</sub> = 25W/Ch, A-weighted              |     | 98   |     | dB     |

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792 WEB:Http://www.ChipSourceTek.com

## **SGM4703 ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 24V, f = 1kHz, Load = 4\Omega + 33\mu H, SSM, PBTL configuration, T_A = +25^{\circ}C, unless otherwise specified.)$

| PARAMETER                         | SYMBOL               | CONDITIONS                                       | MIN | TYP | MAX | UNITS |

|-----------------------------------|----------------------|--------------------------------------------------|-----|-----|-----|-------|

| Peak Output Power <sup>(1)</sup>  | D                    | THD+N = 10%, Non-ALC Mode                        |     | 80  |     | w     |

|                                   | P <sub>O, PEAK</sub> | THD+N = 1%, Non-ALC Mode                         |     | 64  |     | VV    |

| ALC Output Power                  | P <sub>O, ALC</sub>  | V <sub>IN</sub> = 1.0V <sub>RMS</sub>            |     | 60  |     | W     |

| Total Harmonic Distortion + Noise | THD+N                | P <sub>O</sub> = 40W, Non-ALC Mode               |     | 0.1 |     | - %   |

| Total Harmonic Distortion + Noise |                      | V <sub>IN</sub> = 1.0V <sub>RMS</sub> , ALC Mode |     | 0.3 |     |       |

| Power Efficiency (2)              | η                    | P <sub>O</sub> = 40W, Non-ALC Mode               |     | 90  |     | - %   |

| Power Efficiency V                |                      | V <sub>IN</sub> = 1.0V <sub>RMS</sub> , ALC Mode |     | 91  |     |       |

| Signal-to-Noise Ratio             | SNR                  | P <sub>o</sub> = 50W, A-weighted                 |     | 98  |     | dB    |

$(V_{DD}$  = 15V, f = 1kHz, Load = 3 $\Omega$  + 15 $\mu$ H, SSM, PBTL configuration,  $T_A$  = +25 $^{\circ}$ C, unless otherwise specified.)

| PARAMETER                         | SYMBOL               | CONDITIONS                                        | MIN | TYP | MAX | UNITS |

|-----------------------------------|----------------------|---------------------------------------------------|-----|-----|-----|-------|

| TAXAMETER                         | OTHIBOL              |                                                   |     |     | WAX | OMITO |

| Peak Output Power (1)             | P <sub>O, PEAK</sub> | THD+N = 10%, Non-ALC Mode                         | · · | 40  |     | w     |

| I eak Output I owel               | · U, PEAK            | THD+N = 1%, Non-ALC Mode                          |     | 33  |     | "     |

| ALC Output Power                  | P <sub>O, ALC</sub>  | $V_{IN} = 0.60V_{RMS}$                            |     | 30  |     | W     |

| Total Harmonic Distortion + Noise | THD+N                | P <sub>O</sub> = 20W, Non-ALC Mode                |     | 0.1 |     | - %   |

| Total Harmonic Distortion + Noise |                      | V <sub>IN</sub> = 0.60V <sub>RMS</sub> , ALC Mode |     | 0.3 |     | 70    |

| Power Efficiency (2)              | η                    | P <sub>o</sub> = 20W, Non-ALC Mode                |     | 89  |     | - %   |

|                                   |                      | V <sub>IN</sub> = 0.60V <sub>RMS</sub> , ALC Mode |     | 90  |     | 70    |

| Signal-to-Noise Ratio             | SNR                  | P <sub>O</sub> = 30W, A-weighted                  |     | 96  |     | dB    |

$(V_{DD}$  = 12V, f = 1kHz, Load =  $2\Omega$  + 15 $\mu$ H, SSM, PBTL configuration,  $T_A$  = +25 $^{\circ}$ C, unless otherwise specified.)

| PARAMETER                         | SYMBOL               | CONDITIONS                                        |  | TYP | MAX | UNITS |

|-----------------------------------|----------------------|---------------------------------------------------|--|-----|-----|-------|

| Peak Output Power (1)             |                      | THD+N = 10%, Non-ALC Mode                         |  | 37  |     | 10/   |

|                                   | P <sub>O, PEAK</sub> | THD+N = 1%, Non-ALC Mode                          |  | 30  |     | W     |

| ALC Output Power                  | P <sub>O, ALC</sub>  | V <sub>IN</sub> = 0.50V <sub>RMS</sub>            |  | 27  |     | W     |

| Total Harmonic Distortion + Noise | THD+N                | P <sub>0</sub> = 20W, Non-ALC Mode                |  | 0.1 |     | %     |

| Total Harmonic Distortion + Noise |                      | V <sub>IN</sub> = 0.50V <sub>RMS</sub> , ALC Mode |  | 0.3 |     | 70    |

| Power Efficiency (2)              |                      | 0 ,                                               |  | 87  |     | %     |

|                                   | η                    |                                                   |  | 88  |     | 70    |

| Signal-to-Noise Ratio             | SNR                  | P <sub>O</sub> = 25W, A-weighted                  |  | 94  |     | dB    |

#### NOTES:

- 1. The peak output power is defined as an instantaneous maximum output power with no consideration of the thermal dissipation capability of the system board. The maximum continuous output power will be less than the peak output power and largely depend upon the thermal dissipation capability of the system board.

- 2. All the power efficiency data are given for a two-side, two-layer printed circuit board and shall be used for reference only. The power efficiency will be strongly affected by the thermal dissipation capability of the system board, such as the number of layers and the application of a heat sink.

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792 WEB:Http://www.ChipSourceTek.com

#### SGM4703 TYPICAL PERFORMANCE CHARACTERISTICS

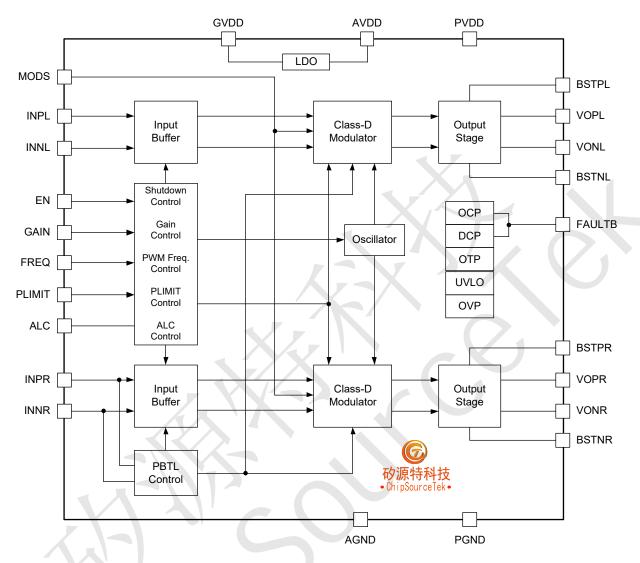

#### SGM4703 FUNCTIONAL BLOCK DIAGRAM

Figure 3. Block Diagram

#### **SGM4703 APPLICATION INFORMATION**

The SGM4703 is a high-power, high-efficiency, stereo Class-D audio power amplifier with adjustable power limit (APL) and automatic level control (ALC). It operates with a wide range of supply voltages from 5V to 26V. With 24V supply voltage, it can deliver 2 × 40W peak output power for a pair of  $8\Omega$  speakers with 10% THD+N.

The high efficiency of SGM4703 extends battery life in playing music and allows it to deliver an output power of 2 × 20W without the need for a bulky heat sink on a two-layer system board. Its high PSRR and low EMI emission reduce system design and manufacturing complexities, as well as thus lower system cost.

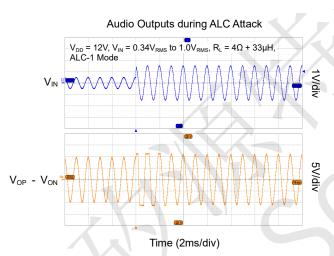

The SGM4703 features APL and ALC. The APL limits peak audio outputs to a user-defined value to protect audio speakers from excessive power dissipation and over-load. The APL and ALC adjust the voltage gain of the audio amplifiers in response to over-limit audio inputs, eliminating output clipping distortion while maintaining a maximally allowed dynamic range of audio outputs. The limiting voltage of APL and ALC can be either the supply voltage or a user-defined value.

The SGM4703 can be configured into driving either a pair of speakers in Bridge-Tied-Load (BTL) configuration for stereo applications or a single speaker in Parallel BTL (PBTL) configuration for mono applications. In PBTL configuration, with 15V supply voltage, it can deliver into a  $3\Omega$  speaker an output power of 33W with 1% THD+N, or an ALC output power of 30W with THD+N less than 0.5%.

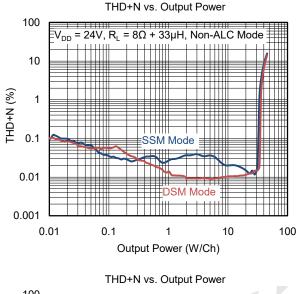

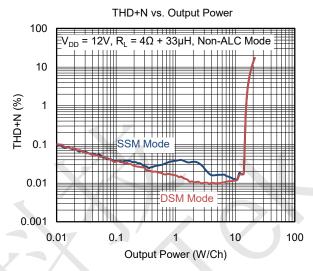

The SGM4703 features two PWM modulation schemes for use in Class-D audio amplifiers: Dual-Side-Modulation (DSM) and Single-Side-Modulation (SSM), allowing for system optimization for higher efficiency or lower THD.

The SGM4703 includes comprehensive protection modes against various operating faults including under-voltage, over-voltage, over-current, over-temperature, and DC-detect for safe and reliable operation.

#### **Operating Mode Control**

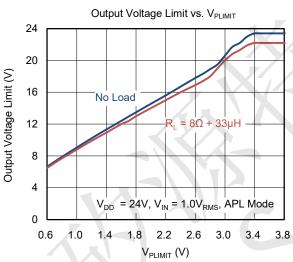

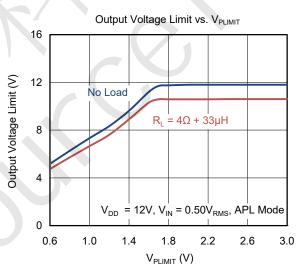

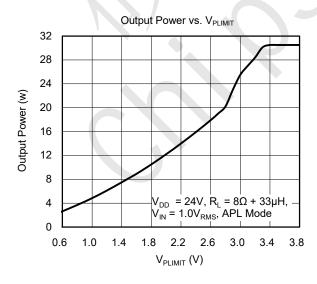

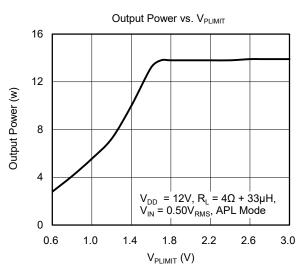

The SGM4703 features APL and ALC modes of operation. In APL mode, peak audio outputs are clamped (hard-limited) to a voltage level defined by the PLIMIT pin, protecting audio speakers from excessive power dissipation and over-load.

As described in Table 1, depending upon the pin voltage at PLIMIT and the pin configuration at ALC, the SGM4703 can be configured into one of four operating modes: Mute, APL, ALC, and Traditional. In SGM4703, the pin voltage at PLIMIT,  $V_{\text{PLIMIT}}$ , defines the limiting voltage of audio outputs for both APL and ALC modes.

If  $V_{\text{PLIMIT}}$  is set less than 0.3V, the device operates in mute mode regardless of the pin configuration at ALC.

If  $V_{\text{PLIMIT}}$  is set higher than 4.5V with the ALC pin unconnected, the device operates in a traditional Class-D mode without APL or ALC. In this mode, the output clipping distortion will occur as peak output voltages reach to the supply voltage PVDD.

If  $V_{PLIMIT}$  is set in the range from 0.7V to 2.5V with the ALC pin connected to ground through an external resistor of  $0k\Omega$ ,  $68k\Omega$ , or  $300k\Omega$ , the device operates in APL mode. The audio outputs in APL mode are limited to a value approximately equal to  $(6 \times V_{PLIMIT})$ .

If  $V_{\text{PLIMIT}}$  is set higher than 4.5V with the ALC pin connected to ground through an external resistor of  $0k\Omega$ ,  $68k\Omega$ , or  $300k\Omega$ , the device operates in ALC mode and the limiting voltage of audio outputs is internally set at the supply voltage. Thus, the peak voltage of audio outputs is limited to a value that is substantially close to PVDD.

**Table 1. Operating Mode Control**

| V <sub>PLIMIT</sub>               | R <sub>ALC</sub> | Mode        | Description                                                       |  |  |

|-----------------------------------|------------------|-------------|-------------------------------------------------------------------|--|--|

| V <sub>PLIMIT</sub> < 0.3V        | X                | Mute        | Audio outputs shorted to PGND.                                    |  |  |

| V <sub>PLIMIT</sub> < 4.5V        | Open             | Х           | Not applicable.                                                   |  |  |

| V <sub>PLIMIT</sub> > 4.5V        | Ореп             | Traditional | No APL and No ALC.                                                |  |  |

| 0.7V < V <sub>PLIMIT</sub> < 3.5V | 0kΩ, 68kΩ, 300kΩ | APL         | Audio outputs limited to a value defined by V <sub>PLIMIT</sub> . |  |  |

| V <sub>PLIMIT</sub> > 4.5V        | to GND           | ALC         | Audio outputs limited to the supply voltage PVDD.                 |  |  |

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792 WEB:Http://www.ChipSourceTek.com

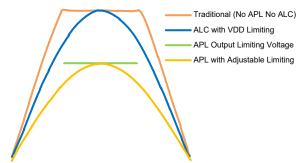

Figure 4 depicts large audio outputs in different operating modes when excessive inputs are applied to cause peak outputs higher than either the supply voltage or a user-defined voltage limit lower than the supply voltage.

Figure 4. Large Audio Outputs in Different Operating Modes

#### **GVDD Supply**

The GVDD is an internally generated supply voltage for internal circuitry. It is also used as the supply voltage for the resistor divider to set the voltage at the PLIMIT pin. It is highly suggested to decouple the GVDD pin with a  $1\mu F$  ceramic capacitor to ground for stable operation. Note that the current drawn from the GVDD pin by external circuitry, including all the resistor dividers at ALC, GAIN, FREQ, and PLIMIT pins, must be kept less than 5mA.

#### **MUTE Control**

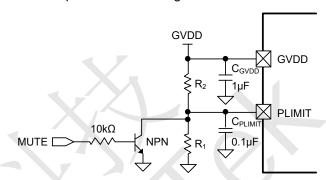

The SGM4703 can be configured into mute mode when the PLIMIT pin is pulled low by an inverting transistor, as shown in Figure 5. In mute mode, the output stages of both audio amplifiers are in Hi-Z and the differential audio outputs (VOPL/R and VONL/R) are pulled to

ground through on-chip resistors respectively. To restore to its normal operation, the output of the inverting transistor is reverted to Hi-Z state, allowing the resistor divider (from GVDD to ground) tapped at the PLIMIT pin to set the voltage limit for APL.

Figure 5. Example Circuit Diagram of Mute Control

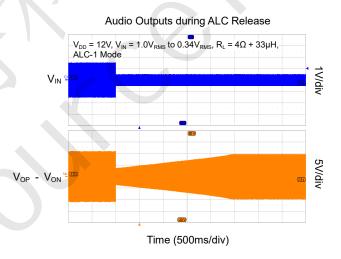

#### **Automatic Level Control (ALC)**

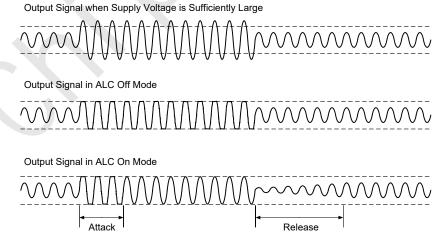

The automatic level control is to maintain the audio outputs for a maximum voltage swing without clip distortion when excessive inputs that may cause output clipping are applied. With ALC, the SGM4703 lowers the voltage gain of both audio amplifiers to an appropriate value such that output clipping is substantially eliminated.

In Figure 6, "Attack" is the duration where the voltage gain of the audio amplifiers decreases until output clipping is substantially eliminated. "Release" is the duration where the voltage gain of the audio amplifiers recovers (increases) until it reaches to a value that is maximally allowed without output clipping.

Figure 6. Automatic Level Control Diagram

#### **ALC Mode Select**

The SGM4703 can be configured into ALC or Non-ALC mode via the ALC pin, as described in Table 2. When the ALC pin is left unconnected, the SGM4703 operates in Non-ALC mode. The Non-ALC mode is typically chosen for applications where maximum audio loudness is desired and the amount of output clipping distortions can be measurably controlled at the audio source. In other pin configurations, the SGM4703 operates in ALC mode with three specific audio dynamic characteristics. For most applications, the ALC mode is preferred for its capability to substantially

eliminate output clipping distortion, excessive power dissipation, and speaker over-load.

Three sets of ALC dynamic characteristics can be selected for specific sound effects, as described in Table 2. The ALC-1 mode (the ALC pin shorted to GND) plays music in a most mellow manner with negligible amount of clipping distortion and lower average output power. On the other hand, the ALC-3 mode (the ALC pin shorted to GND via a  $300 \mathrm{k}\Omega$  resistor) plays music in a most dynamic manner with some extent of clipping distortion and higher average output power (loudness).

**Table 2. ALC Mode Select**

|                                |                                                                          | Sound Effects                                   |                               |  |  |  |  |  |  |

|--------------------------------|--------------------------------------------------------------------------|-------------------------------------------------|-------------------------------|--|--|--|--|--|--|

| ALC ALC Pin Configuration Mode |                                                                          |                                                 |                               |  |  |  |  |  |  |

| <b>33</b>                      |                                                                          | Loudiless                                       | Output Clipping Distortion    |  |  |  |  |  |  |

| Open                           | Non-ALC                                                                  | Potentially highest loudness                    | No control on output clipping |  |  |  |  |  |  |

| Shorted to GND                 | ALC-1                                                                    | Most mellow sound (Lowest loudness under ALC)   | Negligible output clipping    |  |  |  |  |  |  |

| 68kΩ to GND ALC-2              |                                                                          | Medium loudness                                 | Slight output clipping        |  |  |  |  |  |  |

| 300kΩ to GND                   | ALC-3                                                                    | Most dynamic sound (Highest loudness under ALC) | Acceptable output clipping    |  |  |  |  |  |  |

| Note: The resistor tole        | lote: The resistor tolerance of R <sub>ALC</sub> should be 5% or better. |                                                 |                               |  |  |  |  |  |  |

#### Voltage Gain Setting

To accommodate various application requirements, the SGM4703 features four selectable voltage gains for audio amplifiers. An external resistor  $R_{\text{GAIN}}$  from the GAIN pin to ground sets the voltage gain, as shown in Table 3.

Table 3. Voltage Gain Select

| GAIN<br>Pin<br>Configuration                                              | R <sub>INI</sub> (kΩ) | A <sub>V</sub> (V/V) | A <sub>V</sub> (dB) |  |  |  |  |

|---------------------------------------------------------------------------|-----------------------|----------------------|---------------------|--|--|--|--|

| Open                                                                      | 30                    | 20                   | 26                  |  |  |  |  |

| Shorted to GND                                                            | 20                    | 30                   | 30                  |  |  |  |  |

| 68kΩ to GND                                                               | 12                    | 50                   | 34                  |  |  |  |  |

| 300kΩ to GND                                                              | 60                    | 10                   | 20                  |  |  |  |  |

| Note: The resistor tolerance of R <sub>GAIN</sub> should be 5% or better. |                       |                      |                     |  |  |  |  |

Although the voltage gains as described in Table 3 vary a little (less than 2%) from parts to parts, the input impedances at the same voltage gain may vary by  $\pm 20\%$  over parts, due to process variations in the actual resistance of the input resistors. For design purposes, the input impedance should be assumed to be  $10k\Omega$ , which is the absolute minimum input impedance of the audio amplifiers in SGM4703. At lower gain settings, the input impedance could be as high as  $60k\Omega$ .

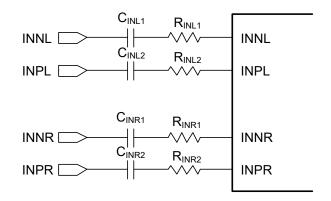

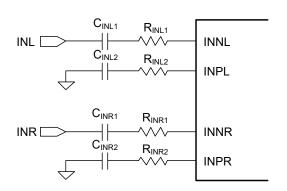

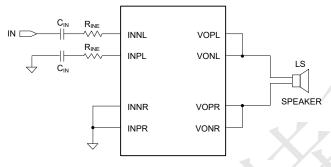

The voltage gain of the audio amplifiers can be slightly adjusted by inserting small external input resistors  $R_{\text{INE}}$ , in series with the input capacitors  $C_{\text{IN}}$ , as depicted in Figure 7 and Figure 8 for differential and single-ended inputs respectively. In the figures, it is required that  $C_{\text{IN}} = C_{\text{INL1/2}} = C_{\text{INR1/2}}$  and  $R_{\text{INE}} = R_{\text{INL1/2}} = R_{\text{INR1/2}}$ .

As depicted in Figure 8, the unused inputs of SGM4703 in single-ended inputs applications must be AC-grounded at the audio source. Also, take care to match the impedances of the two differential inputs.

Figure 7. Gain Setting (Differential Inputs)

Figure 8. Gain Setting (Single-Ended Inputs)

The value of  $R_{\text{INE}}$  (in  $k\Omega)$  for a given voltage gain can be calculated by Equation 1, where  $A_{\text{V}}$  is the voltage gain of the audio amplifier.

$$A_{V} = \frac{600}{R_{INE} + R_{INI}} \tag{1}$$

The choice of the voltage gain will strongly influence the loudness and quality of audio sounds. In general, the higher the voltage gain is, the louder the sound is perceived. However an excessive voltage gain may cause audio outputs to be severely clipped (Non-ALC mode) or compressed (ALC mode) for high-level (loud) audio sounds. On the other hand, an unusually low gain may cause relatively low-level (quite) sounds soft or inaudible. Thus it is crucial to choose a proper voltage gain for well balanced audio quality.

The voltage gain is chosen based upon various system-level considerations including the supply voltage, the dynamic range of audio sources and speaker loads, and the desired sound effects. As a general guideline, the voltage gain can be simply expressed in Equation 2. In the equation,  $V_{\text{IN, MAX}}$  (in  $V_{\text{RMS}}$ ) is the maximum input level from the audio source, PVDD (in volts) is the supply voltage, and  $\alpha$  is the design parameter, which ranges from 0.66 to 1.0. The higher  $\alpha$  is, the higher the average output power (louder) is, with some degree of compression for high-level audio sounds.

$$A_{V} = \frac{\alpha \times PVDD}{V_{IN MAX}}$$

(2)

As an example, Table 4 shows the voltage gain for various input levels with PVDD at 12V and 18V and  $\alpha$  at about 0.80. In the table,  $R_{\text{INE}}$  is the external input resistor in series with the input capacitor and  $R_{\text{INI}}$  is the internal input resistor.

Table 4. Typical Voltage Gain Settings for Various  $V_{\text{DD}}$  & Audio Input Levels

| V <sub>IN, MAX</sub> (V <sub>RMS</sub> ) | A <sub>V</sub><br>(V/V) | A <sub>V</sub><br>(dB) | $R_{GAIN}$ to GND ( $k\Omega$ ) | R <sub>INI</sub><br>(kΩ) | R <sub>INE</sub><br>(kΩ) |  |

|------------------------------------------|-------------------------|------------------------|---------------------------------|--------------------------|--------------------------|--|

| $V_{DD} = 12^{\circ}$                    | V                       |                        |                                 |                          |                          |  |

| 0.5                                      | 20                      | 26                     | Open                            | 30                       | 0                        |  |

| 0.7                                      | 13.3                    | 22.5                   | Open                            | 30                       | 15                       |  |

| 1.0                                      | 10                      | 20                     | 300                             | 60                       | 0                        |  |

| V <sub>DD</sub> = 18V                    |                         |                        |                                 |                          |                          |  |

| 0.5                                      | 30                      | 29.5                   | 0                               | 20                       | 0                        |  |

| 0.7                                      | 20                      | 26                     | Open                            | 30                       | 0                        |  |

| 1.0                                      | 15                      | 23.5                   | Open                            | 30                       | 10                       |  |

| $V_{DD} = 24^{\circ}$                    | V                       |                        |                                 |                          |                          |  |

| 0.5                                      | 40                      | 32                     | 68                              | 12                       | 3.0                      |  |

| 0.7                                      | 28.5                    | 29                     | 0                               | 20                       | 1.0                      |  |

| 1.0                                      | 20                      | 26                     | Open                            | 30                       | 0                        |  |

#### **PWM Frequency Setting**

To accommodate various application requirements, the SGM4703 features two selectable PWM frequencies with optional spread-spectrum for the Class-D audio amplifiers. An external resistor  $R_{\text{FREQ}}$  from the FREQ pin to ground sets the PWM frequency and optional spread-spectrum, as shown in Table 5.

Table 5. PWM Frequency Select with Optional Spread-Spectrum

| FREQ<br>Pin Configuration                                                 | PWM Frequency<br>(kHz) | Spread-Spectrum |  |  |  |  |  |

|---------------------------------------------------------------------------|------------------------|-----------------|--|--|--|--|--|

| Open                                                                      | 360                    | No              |  |  |  |  |  |

| Shorted to GND                                                            | 360                    | Yes             |  |  |  |  |  |

| 68kΩ to GND                                                               | 500                    | No              |  |  |  |  |  |

| 300kΩ to GND                                                              | Yes                    |                 |  |  |  |  |  |

| Note: The resistor tolerance of R <sub>FREQ</sub> should be 5% or better. |                        |                 |  |  |  |  |  |

#### **PWM Modulation Scheme**

To accommodate various application requirements, the SGM4703 features two PWM modulation schemes, i.e., Single-Side-Modulation (SSM) and Double-Side-Modulation (DSM). In typical applications, the SSM scheme is preferred for its lower EMI and higher PSRR and efficiency. The modulation scheme is selected via the MODS pin, as described in Table 6. The PWM modulation scheme is latched during power-up and cannot be changed while the device is in operation.

**Table 6. Modulation Scheme Select**

| MODS         | Modulation Scheme |

|--------------|-------------------|

| High or Open | SSM               |

| Low          | DSM               |

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792 WEB:Http://www.ChipSourceTek.com

#### **Double-Side-Modulation (DSM)**

With DSM scheme, during an idle condition (no audio signal applied), both VOPL/R and VONL/R outputs are at 50% duty cycle and in phase with each other, resulting in little or no current flowing through the speaker. When a positive audio input is applied, the duty cycle of VOPL/R is greater than 50% and VONL/R is less than 50%, resulting in a positive current flowing through the speaker. When a negative audio input is applied, the duty cycle of VOPL/R is less than 50% and VONL/R is greater than 50%, resulting in a negative current flowing through the speaker. Compared with the traditional modulation scheme, the DSM scheme reduces the switching current, which minimizes any I<sup>2</sup>R losses in the speaker load and eliminates the need for an LC output filter for most applications.

#### Single-Side-Modulation (SSM)

The SSM scheme alters the DSM scheme in order to achieve higher efficiency with a slight penalty in THD degradation and more attention required for the selection of the output filter. With SSM scheme, the audio outputs operate with less than 10% modulation during an idle condition. When an audio signal is applied, one output will decrease and another one will increase. The decreasing output signal will quickly rail to ground at which point all the audio modulation takes place through the rising output. The result is that only one output is switching during a majority of the audio cycle. Efficiency is improved with SSM scheme due to the reduction of switching losses. The THD penalty with SSM scheme is minimized by the on-chip linear feedback loop.

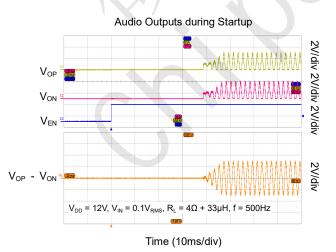

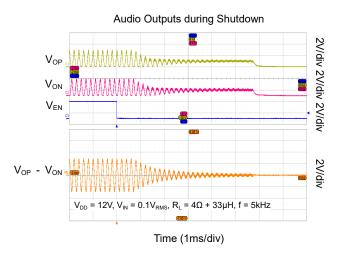

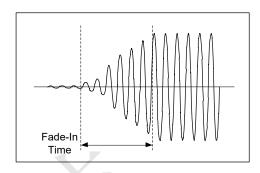

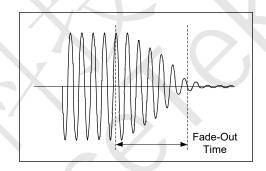

#### Volume Fade-In and Fade-Out

The SGM4703 features volume fade-in and fade-out to reduce intermittent sound and eliminate uncomfortable hearing experience during the transitions when the device enters or exits the normal operation. Figure 9 and Figure 10 show the audio output waveforms during fade-in and fade-out respectively.

Figure 9. Fade-In Waveform

Figure 10. Fade-Out Waveform

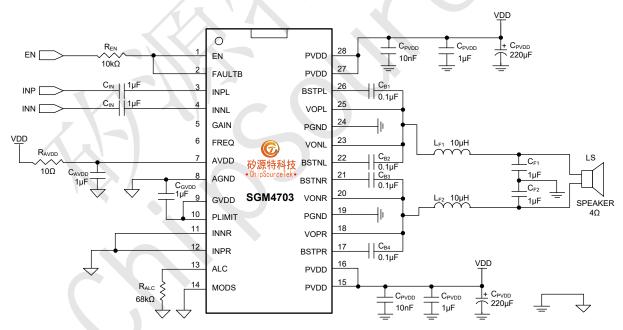

#### **PBTL Configuration (Mono Mode)**

The SGM4703 features an optional mono mode that allows the left and right channels to operate in parallel BTL configuration. To operate the SGM4703 in mono mode, connect the INNR and INPR pins (pin 11 and 12) directly to ground (no decoupling capacitors). In mono mode, as shown in Figure 11, an audio input signal applied to the left channel (pin 3 and 4) is routed to the H-bridge of both channels. Note that the mono mode is intended to be configured strictly by the hardware connection. Leaving either INNR or INPR pin unconnected while the audio outputs VOPL/R and VONL/R are wired together in PBTL configuration can trigger an over-current or thermal overload protection or both. The mono mode is configured by the following arrangement:

- Connect INPR and INNR pins directly to ground (no decoupling capacitors).

- Connect VOPL to VONL together as one terminal of the speaker and connect VOPR to VONR together as the other terminal of the speaker. Use heavy PCB traces as close as possible to the device.

- Place the speaker between the left and right-channel outputs.

- Apply an audio signal to the left-channel inputs (INPL and INNL pins).

Figure 11. PBTL Configuration for Mono Applications

#### Click-and-Pop Suppression

The SGM4703 features comprehensive click-and-pop suppression. During startup, the click-and-pop suppression circuitry reduces any audible transients internal to the device. When entering into shutdown, the differential audio outputs VOPL/R and VONL/R ramp down to ground quickly and simultaneously.

#### **PSRR Enhancement**

Without a dedicated pin for the common-mode voltage bias and an external holding capacitor onto the pin, the SGM4703 achieves a PSRR, 80dB at 1kHz with SSM scheme.

#### Startup and Shutdown

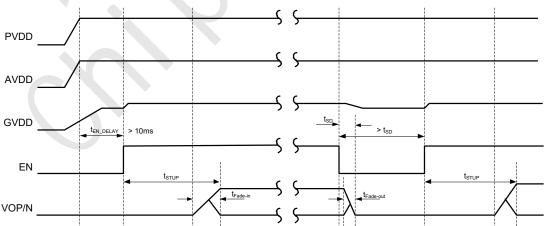

The SGM4703 requires a power-up sequence (see Figure 12). Please hold EN low at least 10ms after PVDD and AVDD supply voltages are turned on.

The SGM4703 employs the EN pin to minimize power consumption when not in use. When the EN pin is pulled low, the SGM4703 is forced into shutdown mode. At this time, all the analog circuitry is de-biased and the supply current is reduced to less than  $60\mu A$ , and the differential outputs are shorted to ground through an on-chip resistor  $(5k\Omega)$  individually. Once in shutdown mode, the EN pin must remain low for at least  $10ms(t_{SD})$  for the shutdown settling time before it can be pulled high again. When the EN pin is asserted high, the device exits out of shutdown mode and enters into normal operation after the startup time  $(t_{STUP})$  of 45ms.

An on-chip pull-down resistor of  $250k\Omega$  is included onto the EN pin. Thus, shutdown mode is the state when the power supply is first applied to the device. Whenever possible, please hold the EN pin low until the device is properly powered up and the audio signals at the inputs are stable. Also, for best power-off pop performance, place the device in shutdown mode prior to removing the power supply voltage.

Note that the setting at the MODS pin is latched during startup and cannot be changed while the device is in operation. To change the setting of the MODS pin, the device must be first brought into shutdown mode by pulling the EN pin low for at least 10ms before it can be restored to its normal operation.

Figure 12. Startup Timming

TEL: +86-0755-27595155 27595165 FAX: +86-0755-27594792 WEB:Http://www.ChipSourceTek.com

#### **Protection Modes**

For safe operation, the SGM4703 incorporates comprehensive protection circuits against various operating faults including Under-Voltage, Over-Current, Over-Temperature, and DC-Detect, as described in Table 7. In the shutdown mode, all the analog circuitry is de-biased with differential outputs to be shorted to ground. In the mute mode, all the analog circuitry is enabled with differential outputs to be shorted to ground.

#### **Under-Voltage Lockout (UVLO)**